# High Speed Surface Illuminated Si Photodiode Using Microstructured Holes for Absorption Enhancements at 900–1000 nm Wavelength

Yang Gao,<sup>†</sup> Hilal Cansizoglu,<sup>†</sup> Soroush Ghandiparsi,<sup>†</sup> Cesar Bartolo-Perez,<sup>†</sup> Ekaterina Ponizovskaya Devine,<sup>§</sup> Toshishige Yamada,<sup>‡</sup> Aly F. Elrefaie,<sup>†,§</sup> Shih-yuan Wang,<sup>§</sup> and M. Saif Islam<sup>\*,†</sup>

<sup>†</sup>Electrical and Computer Engineering, University of California, Davis, Davis, California 95618, United States

<sup>‡</sup>Electrical Engineering, Baskin School of Engineering, University of California, Santa Cruz, Santa Cruz, California 95064, United States

<sup>§</sup>W&WSens Devices, Inc., 4546 El Camino, Suite 215, Los Altos, California, United States

**S** Supporting Information

**ABSTRACT:** A surface-illuminated silicon photodiode with both high speed and usable external quantum efficiency from 900 to 1000 nm wavelength is highly desirable for intra/inter data center Ethernet communications, high performance computing, and laser radar application. Such Si photodiodes have the potential for monolithic integration to CMOS integrated circuits which can significantly reduce the cost of data transmission per gigabit below one US dollar. To overcome silicon's intrinsic weakness of absorption in these wavelengths, photon-trapping microstructured hole arrays are etched into the silicon surface, and the operational wavelengths of a high-speed silicon PIN photodiode are extended to 1000 nm. In this paper, the design and fabrication of such photon-trapping structures integrated into all-silicon photodiodes with significantly reduced absorption layer thicknesses to achieve high external quantum efficiency and fast response are presented. Different designs and geometries of the submicron holes on the silicon surface can affect the light trapping and ultimately contribute to different external quantum efficiencies at these wavelengths. Some designs are capable of enhancing the absorption by more than an order of magnitude compared to a photodiode without the submicron hole arrays. With the silicon *i*-layer thickness less than or equal to 2  $\mu$ m, the all-silicon photodiode with integrated submicron holes exhibited an external quantum efficiency of more than 40% at 900 nm and greater than 15% at 1000 nm. This thin absorption layer also allows the fast speed of the photodiode with temporal responses of  $\sim$ 30 ps at these wavelengths.

KEYWORDS: photon-trapping, microstructure holes, high quantum efficiency, high speed, all-silicon photodiode

With increasing data rates of 10, 25, 50, and 100 Gb/s and beyond, the use of a single wavelength at 850 nm for short reach optical data communication cannot satisfy the demands of modern data centers and high performance computing (HPC). Short wavelength division multiplexing (SWDM) is becoming more common as many as 4 to 5 wavelength ranges are piped into a single multimode optical fiber.<sup>1,2</sup> The wavelengths can range from 850 to 940 nm, for example, 850, 880, 910, and 940 nm, according to the Multi Source Agreement for 100 Gb/s Ethernet application.<sup>3-6</sup> An additional wavelength at 980 nm was also proposed.<sup>4</sup> Another application is HPC systems, which covers wavelengths of 990, 1015, 1040, and 1065 nm.<sup>5,7,8</sup> In addition, laser radar (LIDAR or LADAR) systems use a wide range of wavelengths, for example, 850 and 905 nm for automobile application<sup>9</sup> and 1065 nm for 3D topographic imaging application.<sup>10</sup> In the optical link systems, the traditional photodiode of choice is an AlGaAs/GaAs or InGaAs/InP photodiode. Such photodiodes are made from direct bandgap materials and offer high external

Received:

May 14, 2017

Published:

July 18, 2017

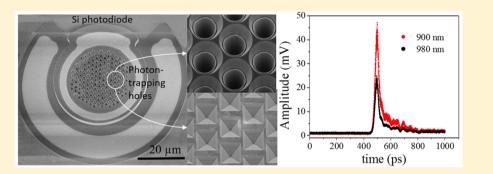

Figure 1. (a) Schematics showing that the vertical incident light transforms to lateral propagating waves in silicon enabled by the periodic submicron holes; (b) Schematics of holes in hexagonal lattice pattern, showing the location of cross-section plane for simulation in (c) and the unit cell in (d) which consists of a complete hole in the center and four 1/4 of holes in the corners; (c) FDTD numerical simulations showing the normalized electric field density distribution around the cross-section of the funneled holes with different sidewall angles (61°, 68°, 83°, and 90°) under top illumination with a wavelength of 980 nm. The white dashed lines represent the boundaries of the holes, and the color scale represents the normalized electric field distribution; (d) Top view of poynting vectors of the light energy around the holes with different angles under vertical optical illumination at the wavelength of 980 nm after 104 fs. The blue arrows represent the energy flux direction and the color scales represent the normalized energy flux densities. White dashed circles represent the boundaries of the submicron holes, "d" represents the diameter of the submicron holes, and "p" represents the period between the submicron holes. The absorption *i*-layer thickness is 2  $\mu$ m in (c) and (d).

quantum efficiencies (EQE). However, they cannot be monolithically integrated with silicon and require hybrid integration such as wafer bonding and wire bonding in order to be integrated into silicon (Si) electronic chips.<sup>11</sup> None of the integration techniques are conducive to high volume production on 12 in. silicon wafers.

Silicon photodiodes are not used traditionally due to its weak absorption coefficient at the near-infrared wavelengths close to silicon bandgap wavelength (1.1  $\mu$ m). At 300 K, the absorption coefficient of silicon drops from 4140 cm<sup>-1</sup> at the wavelength of 600 nm to just 535 cm<sup>-1</sup> at the wavelength of 850 nm, and further to 95.9 cm<sup>-1</sup> at the wavelength of 980 nm.<sup>12</sup> These optical properties have limited the application of silicon photodiodes mostly in the visible and near-infrared wavelength regime with a bandwidth of less than 3 Gb/s. For the wavelengths longer than 800 nm, a conventional PIN Si photodiode would need an *i*-layer thickness of more than 10  $\mu$ m to exhibit a reasonable EQE.<sup>13–17</sup> However, in the current silicon photodiode technology, high speed and high efficiency are often a trade-off, since a high-speed device needs thin "intrinsic" absorption layer to reduce the electron-holes pair transit time. To overcome this dilemma, the effective absorption of Si needs to be enhanced without increasing the intrinsic layer thickness to maintain the high-speed performance of the Si photodiodes of 10-25 Gb/s.

Solar cells with micro- and nanostructures have been demonstrated with enhanced absorption<sup>18–25</sup> and the conversion efficiency improvement by  $20-25\%^{19,20,23}$  using photon-trapping techniques. A high speed high efficiency Si PIN photodiode with microstructure holes was also demon-

strated at 850 nm.<sup>26</sup> In this work, wavelengths of 900–1000 nm are addressed and this spectrum is only 100 nm from the band edge of Si. The all-silicon photodiode has the ability to cover all the wavelengths for SWDM applications for 100 Gb/s Ethernet applications, part of the wavelengths for HPC applications and all the wavelengths for automobile LIDAR systems. The quantum efficiency of a silicon photodiode with microstructure holes can be 500% to over 1000% improvement over a similar PIN photodiode without absorption enhancement micro and nanostructures. The clear advantage of silicon photodiodes is the ability for monolithic integration with CMOS electronics such as transimpendance amplifiers (TIA),<sup>27-29</sup> for example. In this paper, the focus is on the design and fabrication aspects of the photon-trapping submicron structures. Different etch methods used to create different shapes and depths of the submicron holes are studied to maximize the EQE of the device. Both simulations and experiments results show that the physical design parameters of the submicron holes including the geometry, the periodic lattice constant, sizes, sidewall angles, and device surface, all collectively affect the photon trapping capability, thus, result in different EQEs for the same intrinsic layer thickness.

# RESULTS AND DISCUSSION

**Theory and Simulations.** In the previous work,<sup>26</sup> it has been shown that due to the 2D periodic holes on the silicon surface, the initial incident vertical plane waves transform to an ensemble of lateral collective modes, and thus, enhance the effective optical path for absorption. This is analogous to the

generated ripple waves as pebble is dropped into a still pool of water. The schematics of the photon-trapping mechanism is shown in Figure 1a. Funnel-shaped holes are used in the simulation in this work to reflect the actual etch geometry of the holes from the fabrication process as will be described later in this paper. Different opening angles (indicated as shown in Figure 1b) of the funnel-shaped holes are simulated by applying finite-difference time domain (FDTD) method. A plane-wave  $(\lambda = 900-1000 \text{ nm})$  source is incident on the structures from the top. To model the infinite periodic arrays of nanostructures, periodic boundary conditions (PBC) are used at the lateral boundaries; while perfectly matched layers (PML) are used for top and bottom walls of simulation region. To calculate the absorption, light reflection  $R(\lambda)$  and transmission  $T(\lambda)$  are obtained from the hole arrays, and the absorption can be achieved by  $A(\lambda) = 1 - (T(\lambda) + R(\lambda))$ . Only simulations of the funnel shaped holes are presently here, with a diameter (d) of 700 nm, and a period (p) of 1000 nm in 2D hexagonal lattice pattern, as shown in Figure 1b. The holes are 2.5  $\mu$ m deep and consist of 2  $\mu$ m absorption intrinsic "i" layer.

Figure 1c shows that, regardless of the opening angles, the periodic holes arrays can support a set of modes in both vertical and lateral directions at wavelength of 980 nm. Figure 1d shows that at the wavelength of 980 nm, the poynting vector is directed laterally from the holes into adjacent silicon, which means that the light propagates in the lateral direction and then remains confined in Si until it gets absorbed. Since our photodiodes have much larger diameters (30-100  $\mu$ m in the lateral direction) than the *i*-layer thickness (vertical direction), the laterally propagating waves can be absorbed efficiently for wavelengths between 900 and 1000 nm. The EQE of the holes based photodiodes, thus, can be greatly enhanced compared to the device without photon-trapping holes. It should also be noted that both electric fields and poynting vectors simulations point out the potential advantages of using holes with smaller sidewall angles: the normalized electric filed and energy flux density are stronger in holes with smaller sidewall angles (61° and  $68^{\circ}$ ) compared to the ones with larger sidewall angles ( $83^{\circ}$ and 90°).

To compare with the experimentally measured EQE, the absorption only taking place in the 2  $\mu$ m *i*-layer region is considered as the simulated EQE values in these photodiodes. Figure S1 in the Supporting Information, section S1 illustrates the simulated EQE of the photodiodes with funneled holes of different opening angles at the wavelengths between 900 and 1000 nm. It is predicted that by employing the submicron holes, it can significantly improve the EQE by an order of magnitude and extend to the wavelength range of reasonably high EQE even at 1000 nm compared to the photodiodes without any photon-trapping holes.

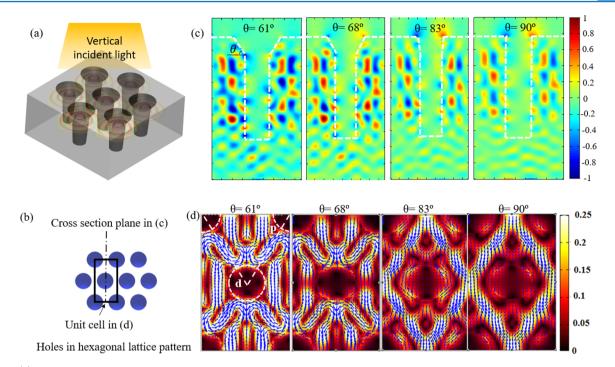

Designs of the Photon-Trapping Holes Based All-Silicon Photodiode. The all-silicon photon-trapping holes based photodiodes have a PIN mesa structure with *n*-Si as the top layer and *p*-Si as the bottom layer as shown in Figure 2a. Different designs of the holes are included in our photodiodes: (1) the submicron holes are in two different lattice patterns: square lattice as shown in Figure 2b and hexagonal lattice, as shown in Figure 2c; (2) the holes have six different designs of diameters (*d*) and periods (*p*): (I) *d/p*: 1300/2000 nm, (II) *d/p*: 1500/2000 nm, (II) *d/p*: 1300/2300 nm; (3) different shapes of the holes are created by nanofabrication dry etch, wet etch and their combination as will be explained later

Article

Figure 2. (a) SEM images of submicron holes based all-silicon photodiodes with mesa structures (the thinner ring is *n*-ohmic metal on *n*-mesa, and the thicker opened ring is the *p*-ohmic metal on *p*-mesa). (b) Top view SEM image of patterned holes in square lattice. (c) Top view SEM image of patterned holes in hexagonal lattice. The white dashed lines in (b) and (c) represent the lattice lines in a unit cell, "d" represents the diameter of the submicron holes, and "p" represents the period between the submicron holes.

in this paper. These different designs are compared to obtain the optimal performance of the photodiodes at wavelengths between 900 and 1000 nm.

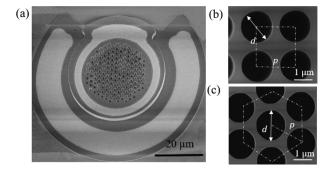

The photodiodes' PIN layers are epitaxially grown on the 0.25  $\mu$ m thick *p*-type device layer on a SOI substrate. The device response time with respect to delta-function-like input light illumination is limited by (1) the electron and hole drift process inside the *i*-layer (~10<sup>1</sup> ps) and (2) the minority carrier diffusion and recombination processes in the *p*- and *n*-layers (~10<sup>2</sup> ps). To reduce the minority carriers' lifetime and make the recombination faster in (2) resulting in faster device response, both *n* and *p* layers are heavily doped. A boron-doped (5 × 10<sup>20</sup> cm<sup>-3</sup>) SiGeB layer is used as a *p*-type contact layer (labeled as *p*+ layer in Figure 3), and a phosphorus-doped (10<sup>19</sup>)

**Figure 3.** Carrier concentration profile of the fabricated photodiode device measured by two-point spreading resistance technique. The intrinsic layer thickness is less than the designed 2  $\mu$ m due to the dopant diffusion from highly doped p+ and n+ layers.

cm<sup>-3</sup>) Si layer is used as an *n*-type contact layer (labeled as *n*+ layer in Figure 3). The *i*-layer is left undoped but turned out to be very slightly *n*-type doped ( $\leq 5 \times 10^{16}$  cm<sup>-3</sup>) in our devices. The *i*-layer has a designed thickness of 2  $\mu$ m, but due to the diffusion of the dopant atoms from *n*+ and *p*+ layers, transition layers are formed next to the *i* layer (labeled as *n*- and *p*- in Figure 3, respectively). They are 0.2 and 0.65  $\mu$ m thick, respectively, and result in reduced thickness of the *i*-layer (<1.6  $\mu$ m). Fortunately, it does not cause any serious problem in this initial series of experiments reported in this paper.

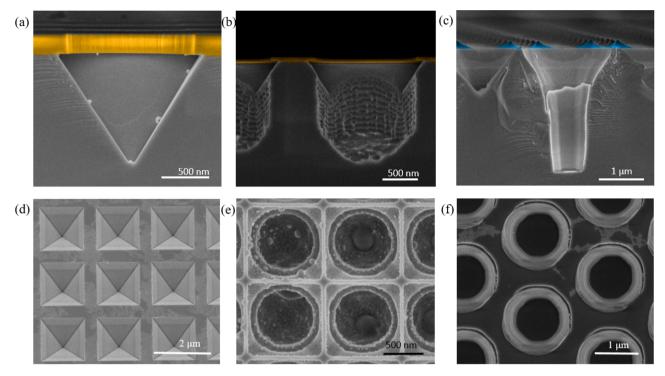

**Figure 4.** Cross-sectional SEM images of (a) holes with sidewall angle of  $54.7^{\circ}$  by wet KOH etch with 300 nm patterned PECVD silicon nitride hardmask (in brown color); (b) holes by wet KOH etch followed by DRIE dry etch with 60 nm patterned PECVD silicon nitride hardmask left on the surface (in brown color). The tapering angle of the holes at the opening is created by KOH, and the straight sidewall is created by DRIE; (c) 3  $\mu$ m deep holes etched by RIE with pyramid shaped DUV resist (in blue color) formed at the holes spacing. (The design of the holes is 1300 nm in diameter and 2000 nm in period (d/p = 1300/2000 nm) arranged in square lattice in (a) and (b), and in hexagonal lattice in (c).) (d-f) Top view SEM images of (a)–(c), respectively (the hardmask or resist are stripped in d–f).

Creating Submicron Holes with Different Geometries and Sidewall Angles. Different etching techniques have been employed to create different geometries and sidewall angles of the submicron holes. The straight submicron holes, as shown in Figure S2, were created using deep reactive ion etch (DRIE), and the details are presented in Supporting Information S2. Isotropic dry etch  $(SF_6$ -based DRIE etch)<sup>30-33</sup> as shown in Figure S3(a) and silicon isotropic wet etch  $(HNO_3/H_2O/NH_4F$  mixed solution)<sup>34,35</sup> as shown in Figure S3(b) can create shallow tapered holes by enabling an undercut beneath the hardmask. The nature of the isotropic etch can easily cause the adjacent holes to interconnect with each other, especially in the holes with smaller periods. These interconnecting holes contribute to a significant materials loss on the sidewall and lead to very low EQEs of the device. This is because the spacing between the holes becomes very thin and any electron-hole pair generated experience higher resistance in constricted structures where surface depletion can impose additional constraints on the transport characteristics.<sup>3</sup>

KOH anisotropic wet etch can form inverted pyramid-shaped holes with a fixed sidewall angle of  $54.7^{\circ}$  in the  $(1\ 0\ 0)$  silicon wafer as Figure 4a shows. The intersection of the  $(1\ 1\ 1)$  plane causes a self-limiting etch and thus the depths of the different holes are determined by the diameter of the holes as Table S1 shows in the Supporting Information S4. In addition, due to the etch rate difference in  $(1\ 0\ 0)$ ,  $(1\ 1\ 0)$ , and  $(1\ 1\ 1)$  planes,<sup>36</sup> the KOH wet etch makes undercut under the silicon nitride mask and forms square inverted pyramid shaped holes as Figure 4d shows even the hardmask pattern is circular.

To extend the depth of the holes by KOH wet etch, another DRIE dry etch is employed after KOH wet etch with existing silicon nitride mask on top as Figure 4b shows. The DRIE dry etch follows the remaining circular nitride hardmask pattern and creates circular shaped holes on the sidewalls of existing KOH etched holes. The combined wet and dry etches create holes with a combination of the square (on top) and circular shapes (at the bottom) as illustrated in Figure 4e. It can also be seen that there is a very abrupt change from  $54.7^{\circ}$  to  $90^{\circ}$  at the sidewall.

KOH wet etch and the combination of KOH and DRIE etches can create holes with tapered angles of 54.7°, neither of holes is deep enough to go through all the silicon intrinsic layer. Another simple dry etch method using reactive ion etch (RIE) is employed in this work, by controlling the resist etch profile, to achieve deeper etched holes with controllable sidewall angle. The detailed process of this method is presented in the Supporting Information S4. As shown in both Figure S4 and Table S2, the DUV resist at the holes spacing undergoes both sidewall profile and thickness changes as the RIE process continues, allowing some lateral etch at the opening of the holes, and finally resulting in the funnel-shaped holes with a depth of 3  $\mu$ m as Figure 4c shows. The hole in Figure 4c has a sidewall angle of  $61^{\circ}$  at the opening and  $83^{\circ}$  at the bottom. By adjusting the initial DUV resist coating thickness and RIE process time, the etch holes can be achieved with desired depth and varying sidewall angle (between  $61^{\circ}$  and  $83^{\circ}$ ) at the opening of the holes. It is able to use an empirical way to estimate the sidewall angle degree by examining the top view SEM images without cleaving the sample, and the details are presented in Supporting Information S6.

Dry etch can cause damages to the silicon surfaces due to the physical ion bombardment and these damaged surfaces can

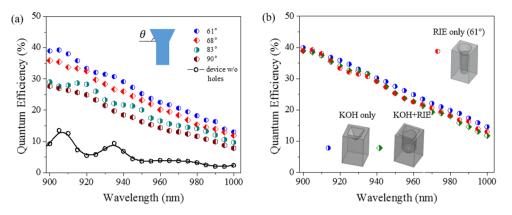

**Figure 5.** (a) Experimentally measured EQE of photodiodes with funneled submicron holes (d/p = 700/1000 nm, hexagonal lattice) of different angles and photodiodes without holes at wavelengths between 900 and 1000 nm: left-filled blue circles, 61°; left-filled red circles, 68°; right-filled green circles, 83°; left-filled brown circles, 90°; and O represent photodiodes without holes. (The inset shows the schematics of the funnel shaped holes with the angle of  $\theta$ .) (b) Experimentally measured EQE of photodiodes with submicron holes (d/p = 700/1000 nm, hexagonal lattice) of different geometries etched by different fabrication techniques: left-filled red circles, funnel-shaped holes by RIE with sidewall angle of 61°; right-filled blue circles, inverted pyramids shaped holes by KOH wet etch; right-filled green triangles, integrated holes by combined KOH wet etch and DRIE dry etch. (The inset shows the 3D schematics of three types of the holes.)

serve as the defect sites and thus lead to undesirable surface states, traps and recombination sites<sup>37,38</sup> which would degrade the photodiodes' detection sensitivity and energy conversion efficiency. In this work, diluted hydrogen fluoride solution  $(HF/H_2O = 1:10)$  or silicon isotropic wet etchant  $(HNO_3/$ H<sub>2</sub>O/NH<sub>4</sub>F mixed solution) is used for 10 s to remove DRIE and RIE associated surface damages of Si.<sup>39</sup> HF can provide hydrogen atoms to the dangling bonds at the Si surface and reduces these dangling bonds and metallic paths<sup>40</sup> and, hence, lowers the trapped charges at the surface. On the other hand, the silicon isotropic wet etchant can totally etch off these damaged silicon surfaces. Our results have shown that both methods are effective to passivate the dry etched silicon surfaces and minimize the leakage current of the photontrapping holes based photodiodes by almost 2 orders of magnitude as shown in Figure S5 in the Supporting Information S7.

Factors Affecting the EQE of the Device. 1. Sidewall Angles. Figure 5a shows the experimentally measured EQEs from photodiodes with holes (d/p = 700/1000 nm) in hexagonal lattice of different sidewall angles which are labeled with different colors. The holes with 90° angle are straight holes created by DRIE, while the RIE etched funneled holes with of 61°, 68°, and 83° were created via different DUV resist coating thickness and varying RIE time. The black circles in Figure 5a represent the measured EQEs of photodiodes without holes. The EQE measurements reveal that photodiodes with submicron holes outperform their counterparts without holes regardless of the sidewall angles. At the wavelength of 900 nm, the EQEs of the photodiodes with submicron holes are 28-40%, whereas the photodiode without micronanostructures is less than 10%. At another data communication wavelength of 980 nm, EQEs of the holes enabled photodiode are 10-20%, while the photodiode without micronanostructures only has less than 2%. This enhancement of absorption has also been seen in photonic crystal structures based solar cells.<sup>19,21,25,41</sup> In our case, the 10 times of EQE enhancement at the wavelength of 980 nm allows the operational wavelength of all-silicon photodiode extended to such wavelength close to the silicon's band edge. In addition, it also shows that the sidewall angles of the periodic submicron holes can greatly impact the EQE of the

device: the smaller the sidewall angle, the higher EQE of the photodiodes. This is mainly because of the reduced reflection with funneled structure which can allow more coupling of light into the *i*-layer. The index difference at Si–air interface can be reduced by decreasing the amount of Si material in air matrix with those funnel shaped holes. The lower index change at Si–air interface can help light go through the medium instead of reflected back from the surface of the structure. The holes with  $61^{\circ}$  sidewall angle show the highest EQE over the spectrum that covers 900–1000 nm.

2. Different Geometries and Depths. As shown in Figure 4, three types of holes are created with different geometries and sidewall angles by KOH wet etch, the combination of KOH wet etch and DRIE and RIE, respectively. The 3D schematics of these holes are also illustrated in the inset of Figure 5 b. The same designs of the submicron holes (design (III): d/p = 700/1000 nm in a hexagonal lattice pattern) are used for comparison. It can be seen that the EQEs are very similar among the three types of holes between 900 and 1000 nm, with the KOH etched holes having slightly better performance. At the wavelength of 980 nm, the EQEs of holes from KOH etch, combined KOH/DRIE and RIE are 20, 18, and 18.5%, respectively. It should be noted that although the geometries are quite different among these holes, the sidewall angles of the holes are similar: both KOH and combined KOH/DRIE etched holes have a fixed angle of 54.7°, while RIE etched holes have a sidewall angle of  $61^\circ$  at the opening. The depths of the holes for design (III) are quite different among these geometries: RIE etched holes have the depth of more than 2.5  $\mu$ m, KOH etched holes only have depths of 500-600 nm, and combined KOH/ DRIE etched holes can reach to 800-900 nm. This indicates that, as long as the lateral propagating modes can be generated by the periodic holes, the depths of the holes do not seem to affect the EQEs as much as the sidewall angles do. The slightly lower EQE of KOH/DRIE etched holes may be caused by the abrupt angle change on the sidewalls of the holes, which may lead to a slightly different reflection from the surface.

3. Dimensions and Lattice Patterns. Total of 12 cases, including 6 designs in hexagonal and square lattice, are compared at different wavelengths between 850 and 980 nm: (I) d/p = 1300/2000 nm, (II) d/p = 1500/2000 nm, (III) d/p

= 700/1000 nm, (IV) d/p = 630/900 nm, (V) d/p = 1500/2500 nm, (VI) d/p = 1300/2300 nm. The lattice parameter effect on the resonant modes has also been observed in ref 42. In our case, as shown in the Supporting Information S8, the holes in hexagonal lattice pattern have better EQE of the holes in square lattice pattern of the same design. This trend is more obvious at the 850 nm compared to 980 nm.

On the other hand, as shown in Figure S6 in the Supporting Information S8, smaller hole designs III (d/p = 700/1000 nm) and IV (d/p = 630/900 nm) in hexagonal have the highest EQEs among all the designs. Similar observations are also noticed in KOH etched and combined KOH/DRIE holes. This indicates that the light incident on the photodiodes with holes of smaller dimension designs can be more easily trapped and generate the lateral modes to enhance the absorption in the active region at those wavelengths.

When the diameter of the holes is a constant, the period between the two holes is also a factor to consider to achieve the optimal EQEs. In our designs, there is a trend that smaller period generally leads to a slightly better EQE performance of the photodiodes. For hole diameters of 1300 and 1500 nm, designs of I and II with smaller period, outperform designs of VI and V with larger period, respectively. However, the design of the period has to be practical, taking into account of the fabrication variation to avoid the interconnection of adjacent holes.

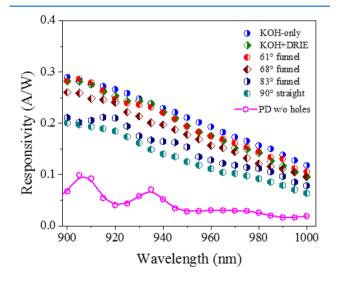

**Responsivity and High Speed.** The device responsivity can be calculated using  $R = \eta \times \frac{\lambda}{1.24}$  (A/W), where *R* is responsivity,  $\eta$  is external quantum efficiency, and  $\lambda$  is the wavelength in  $\mu$ m.

The device responsivities of different holes between 900 and 1000 nm are shown in Figure 6. It can be shown that the inverted holes etched by KOH have the best performance between 900 and 1000 nm among all the holes with the same design (III) with d/p = 700/1000 nm, in a hexagonal pattern. At the wavelengths of 980 and 1000 nm, the responsivities of

Figure 6. Experimentally measured responsivities of photodiodes based on different holes including KOH etched only, KOH/DRIE combination, RIE etched funneled holes with side wall angle of 61°, 68°, and 83°, and straight holes etched by DRIE, compared to photodiodes without any submicron holes between 900 and 1000 nm. The holes' design is (III), with d/p = 700/1000 nm in a hexagonal pattern.

the device with KOH etched holes are around 0.16 and 0.12 A/ W, respectively. They are almost 10-fold of the responsivities of the device without photon-trapping holes. The device responsivity values (measured at 850, 880, 910, and 940 nm) are sufficient to meet the power budget requirements of current SWDM systems.<sup>3</sup> The device can also be used in future SWDM systems using 980 nm as well as HPC and LIDAR systems.

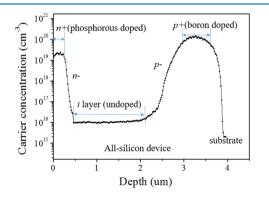

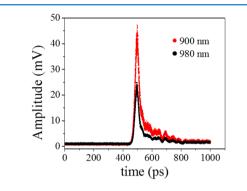

Figure 7 shows the photoresponse of a 30  $\mu$ m photodiode with photon-trapping holes in the form of electrical pulses

**Figure 7.** High-speed responses of a 30  $\mu$ m photodiode with photontrapping holes at the wavelength of 900 nm (red) and 980 nm (black), showing the temporal pulse with fwhm value of 30.3 ps (900 nm) and 30.7 ps (980 nm).

observed on a 20 GHz oscilloscope. The full-width halfmaximum (fwhm) value of the temporal responses above 3 V reverse bias at the wavelengths of 900 and 980 nm are measured to be 30.3 and 30.7 ps, respectively. It should be noted that the peaks of the pulse amplitude are different at these wavelengths, and this is related to the different EQEs at such wavelengths. The temporal responses at other wavelengths are summarized in Table 1. The fast response of the device is capable of supporting both 10G and 25G operations at these wavelengths.

Table 1. Temporal Responses of a 30  $\mu$ m Silicon Photodiode with Photon-Trapping Holes at the Wavelengths between 900 and 1000 nm

| wavelengths (nm) | fwhm (ps) |

|------------------|-----------|

| 900              | 30.3      |

| 950              | 31.1      |

| 980              | 30.7      |

| 990              | 32.7      |

| 1000             | 34.3      |

# CONCLUSION

This study demonstrates the design and fabrication of an allsilicon photodiode with photon-trapping submicron holes structures. These photon-trapping holes successfully enhance the absorption of Si and extend the operational wavelength of the photodiode to 1000 nm with an external quantum efficiency of 20% and responsivity of 0.16 A/W. This represents more than 10-fold increased efficiency compared to Si devices without any photon-trapping holes. The thin intrinsic layer allows this photodiode to be able to operate at ultrahigh speed with a temporal response of  $\sim$ 30 ps at 900 and 980 nm. Multiple parameters of the submicron holes including dimensions, sidewall angles, lattice patterns, and different etch methods affect the absorption in silicon and, thus, lead to considerably different external quantum efficiencies in different photodiodes with different types of holes. We experimentally observed that, among many different designs, photodiodes with periodic funneled holes of 700 nm in diameter and 1000 nm in period, etched via the RIE process, with 61° sidewall angle, and in a hexagonal lattice exhibit the optimal quantum efficiency, as high as 40% at 900 nm. While with the same hole design, an inverted pyramid hole based device etched by KOH exhibits the best quantum efficiency of more than 20% at 980 nm. The devices also show broadband absorption characteristics with high quantum efficiencies between 900 and 1000 nm, which covers all the wavelengths of short wavelength division multiplexing and part of the wavelengths used in high performance computing systems and LIDAR systems. Most importantly, our all-silicon photodiode is fabricated using CMOS compatible processes.

# METHODS

Fabrication of Photon-Trapping Holes Based All-Silicon Photodiode. All the fabrication processes for the photodiodes are CMOS compatible and were done in a class 100 clean room. Briefly, the PIN SOI wafer was precleaned in piranha solution to remove any organic residue. 100 nm of PECVD silicon nitride film was coated on the wafer at 250 °C for KOH etched holes (DRIE and RIE holes are fabricated without the PECVD nitride film). Then, DUV lithography was used to pattern the submicron holes, and then DRIE and RIE were employed to create straight and funneled shape submicron holes, respectively. For KOH etched holes, DRIE was used to pattern the nitride hardmask, and then the wafer was immersed in 24% KOH solution for 2 min at 65 °C. Next, DRIE was used to etch the n-mesa to p-Si layer and p-mesa to the SOI substrate. N-ohmic and p-ohmic metal rings that consist of 100 nm of Al and 20 nm of Pt are deposited on *n*-mesa and *p*-mesa, respectively, by evaporation followed by a lift off process. To minimize the leakage current, the wafer was treated in HF or silicon isotropic etchant for 10 s. Finally, the whole device was passivated with an insulating layer consist of 150/300/150 nm Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> thin layers with contact open. The alternate nitride and oxide layers are used to minimize the effect of possible pinholes and maximize the insulating effect.<sup>43</sup>

**External Quantum Efficiency (EQE) Measurement Setup.** EQE of a photodiode is defined as number of excess electrons per number of incident photons. This definition can be rewritten as following equation:

$$EQE = \frac{I_{\rm ph}/e}{P_{\rm in}/h\varpi}$$

where EQE is the external quantum efficiency,  $I_{\rm ph}$  is photocurrent, *e* is one electron charge,  $P_{\rm in}$  is the incident optical power, and  $h\varpi$  is the energy of a single photon. A supercontinuum laser and a tunable filter that transmits a band of wavelengths with 5 nm width was used to conduct EQE measurements. The light is delivered to the devices by a single-mode fiber probe on a probe station.

**High-Speed Measurement Setup.** A supercontinuum tunable laser source with mode-locking technology has been used to conduct high speed measurements in the wavelength range of 900–1000 nm. The pulse width is sub picosecond (ps) and the repetition rate is 80 MHz. The pulse spectral width is 1-5 nm with a total output average power of 40  $\mu$ W. A device

with a diameter of 30  $\mu$ m is tested with a ground-signal-ground (GSG) microwave probe on a microwave probe station. The light was focused onto the active region of the photodiodes using a single-mode lensed fiber tip and was aligned with a translational stage to maximize the photocurrent.

## ASSOCIATED CONTENT

#### Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsphotonics.7b00486.

Simulated external quantum efficiency (EQE) of photodiodes with funneled holes of different sidewall angles at the opening; Creating straight submicron holes; Isotropic wet etch and dry etch to create shallow tapered holes; KOH wet etch to create inverted pyramid-shaped holes; RIE to create funnel-shaped holes with varying sidewall angles; Estimation of the sidewall angle of RIE etched holes via top view SEM image; Dimension and lattice pattern effect on the EQE at wavelengths of 850 and 980 nm (PDF).

# ■ AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: sislam@ucdavis.edu.

## ORCID 0

M. Saif Islam: 0000-0003-1667-0714

## **Author Contributions**

E.P.D., A.F.E., and S.G. did the simulation. M.S.I., Y.G., H.C., and S.-Y.W. designed the photodiodes. Y.G. and H.C. fabricated the devices. H.C., C.B.P., S.G., and Y.G. carried out the EQE and high-speed characterization of the photodiodes. Y.G., H.C., S.G., A.F.E., and T.Y. discussed the processing and characterization results and analyzed the data. Y.G. drafted the manuscript. S.-Y.W., T.Y., E.P.D., A.F.E., and M.S.I. revised the manuscript. S.-Y.W. and M.S.I. cosupervised this project. All authors have given approval for the final version of the manuscript.

# Notes

The authors declare no competing financial interest.

### ACKNOWLEDGMENTS

We thank S. P. Wang and S. Y. Wang Partnership for financial support. Partial support from ARO (W911NF-14-4-0341) is gratefully acknowledged. We also thank Lawrence Semiconductor Research Laboratories (LSRL) for supplying us epi growth wafers and providing spreading resistance profiles.

#### REFERENCES

(1) Baca, R.; Kolesar, P.; Tatum, J.; Gazula, D.; Shaw, E.; Gray, T. In *Advances in Multimode Fiber Transmission for the Data Center*, Optical Fiber Communications Conference and Exhibition (OFC) 2015; IEEE, 2015; pp 1–3.

(2) Chang, F. First Demonstration of PAM4 Transmissions for Record Reach and High-capacity SWDM Links Over MMF Using 40G/100G PAM4 IC Chipset with Real-time DSP, Optical Fiber Communication Conference; Optical Society of America, 2017; p Tu2B.2.

(3) King, J.; Lewis, D. 100G SWDM4MSA Technical Specifications, Optical Specifications; Finisar, Lumentum, 2017.

(4) Sun, Y.; Lingle, R.; Shubochkin, R.; McCurdy, A. H.; Balemarthy, K.; Braganza, D.; Kamino, J.; Gray, T.; Fan, W.; Wade, K.; Chang, F.; Gazula, D.; Landry, G.; Tatum, J.; Bhoja, S. SWDM PAM4

Transmission Over Next Generation Wide-Band Multimode Optical Fiber. J. Lightwave Technol. 2017, 35, 690–697.

(5) Tan, M. R.; Rosenberg, P.; Sorin, W. V.; Mathai, S.; Panotopoulos, G.; Rankin, G. In *Universal Photonic Interconnect for Data Centers*, Optical Fiber Communication Conference; Optical Society of America, 2017; p Tu2B.4.

(6) King, J.; Lewis, D. 40G SWDM4MSA Technical Specifications, Optical Specifications; Finisar, Lumentum, 2017.

(7) Taubenblatt, M. A. Optical interconnects for high-performance computing. J. Lightwave Technol. 2012, 30, 448–457.

(8) Kuchta, D. In *High-Capacity VCSEL Links*, Optical Fiber Communication Conference; Optical Society of America: 2017; p Tu3C.4.

(9) Rasshofer, R. H.; Spies, M.; Spies, H. Influences of weather phenomena on automotive laser radar systems. *Adv. Radio Sci.* 2011, *9*, 49–60.

(10) Yuan, P.; Sudharsanan, R.; Bai, X.; McDonald, P.; Labios, E.; Morris, B.; Nicholson, J. P.; Stuart, G. M.; Danny, H.; Van Duyne, S.; Pauls, G.; Gaalema, S. Three-dimensional imaging with 1.06um Geiger-mode ladar camera. *Proc. SPIE* **2012**, *8379*, 837902.

(11) Fuad, E.; Doany, C. L. S.; Tsang, C. K.; Ruiz, N.; Horton, R.; Kuchta, D. M.; Patel, C. S.; Knickerbocker, J. U.; Kash, J. A. 300-Gb/s 24-Channel Bidirectional Si Carrier Transceiver Optochip for Board-Level Interconnects. *Elec Comp C* **2008**, 238–243.

(12) Martin, A.; Green, a. M. J. K. Optical Properties of Intrinsic Silicon at 300 K. Prog. Photovoltaics 1995, 3, 189–192.

(13) Zimmermann, H. Integrated Silicon Optoelectronics; Springer, 2010; Vol. 148.

(14) Wieland, J.; Duran, H.; Felder, A. Two-channel 5Gbit/s silicon bipolar monolithic receiver for parallel optical interconnects. *Electron. Lett.* **1994**, *30*, 358–359.

(15) Kyomasu, M. Development of an integrated high speed silicon PIN photodiode sensor. *IEEE Trans. Electron Devices* **1995**, *42*, 1093–1099.

(16) Kim, H. H.; Swartz, R.; Ota, Y.; Woodward, T.; Feuer, M.; Wilson, W. Prospects for silicon monolithic opto-electronics with polymer light emitting diodes. *J. Lightwave Technol.* **1994**, *12*, 2114–2121.

(17) Popp, J.; Philipsborn, H. v. In 10 Gbit/s on-chip photodetection with self-aligned silicon bipolar transistors, ESSDERC'90, 20th European Solid State Device Research Conference, 1990.

(18) Brongersma, M. L.; Cui, Y.; Fan, S. Light management for photovoltaics using high-index nanostructures. *Nat. Mater.* **2014**, *13*, 451–60.

(19) Chen, T.-G.; Yu, P.; Chen, S.-W.; Chang, F.-Y.; Huang, B.-Y.; Cheng, Y.-C.; Hsiao, J.-C.; Li, C.-K.; Wu, Y.-R. Characteristics of large-scale nanohole arrays for thin-silicon photovoltaics. *Prog. Photovoltaics* **2014**, *22*, 452–461.

(20) Han, S. E.; Chen, G. Optical absorption enhancement in silicon nanohole arrays for solar photovoltaics. *Nano Lett.* **2010**, *10*, 1012–5.

(21) Lin, H.; Cheung, H.-Y.; Xiu, F.; Wang, F.; Yip, S.; Han, N.; Hung, T.; Zhou, J.; Ho, J. C.; Wong, C.-Y. Developing controllable anisotropic wet etching to achieve silicon nanorods, nanopencils and nanocones for efficient photon trapping. *J. Mater. Chem. A* **2013**, *1*, 9942.

(22) Garnett, E.; Yang, P. Light trapping in silicon nanowire solar cells. *Nano Lett.* **2010**, *10*, 1082–7.

(23) Zhu, J.; Hsu, C. M.; Yu, Z.; Fan, S.; Cui, Y. Nanodome solar cells with efficient light management and self-cleaning. *Nano Lett.* **2010**, *10*, 1979–84.

(24) Fan, Z.; Razavi, H.; Do, J. W.; Moriwaki, A.; Ergen, O.; Chueh, Y. L.; Leu, P. W.; Ho, J. C.; Takahashi, T.; Reichertz, L. A.; Neale, S.; Yu, K.; Wu, M.; Ager, J. W.; Javey, A. Three-dimensional nanopillararray photovoltaics on low-cost and flexible substrates. *Nat. Mater.* **2009**, *8*, 648–53.

(25) Kuang, P.; Eyderman, S.; Hsieh, M. L.; Post, A.; John, S.; Lin, S. Y. Achieving an Accurate Surface Profile of a Photonic Crystal for Near-Unity Solar Absorption in a Super Thin-Film Architecture. *ACS Nano* **2016**, *10*, 6116–24.

(26) Gao, Y.; Cansizoglu, H.; Polat, K. G.; Ghandiparsi, S.; Kaya, A.; Mamtaz, H. H.; Mayet, A. S.; Wang, Y.; Zhang, X.; Yamada, T.; Devine, E. P.; Elrefaie, A. F.; Wang, S.-Y.; Islam, M. S. Photon-trapping microstructures enable high-speed high-efficiency silicon photodiodes. *Nat. Photonics* **2017**, *11*, 301–308.

(27) Tavernier, F.; Steyaert, M. In Power Efficient 4.5 Gbit/s Optical Receiver in 130 nm CMOS with Integrated Photodiode, Solid-State Circuits Conference, 2008, ESSCIRC 2008, 34th European; IEEE, 2008; pp 162–165.

(28) Momeni, O.; Hashemi, H.; Afshari, E. A 10-Gb/s Inductorless Transimpedance Amplifier. *IEEE Trans. Circuits Syst.: Express Briefs* **2010**, 57, 926–930.

(29) Momeni, O.; Afshari, E. In A High Gain 107 GHz Amplifier in 130 nm CMOS, Custom Integrated Circuits Conference (CICC), IEEE, 2011; pp 1–4.

(30) Ayon, A. A.; Braff, R. A.; Bayt, R.; Sawin, H. H.; Schmidt, M. A. Influence of coil power on the etching characteristics in a high density plasma etcher. *J. Electrochem. Soc.* **1999**, *146*, 2730–2736.

(31) Ngo, H.-D.; Hiess, A.; Seidemann, V.; Studzinski, D.; Lange, M.; Leib, J.; Shariff, D.; Ashraf, H.; Steel, M.; Atabo, L.; Reast, J. Plasma Etching of Tapered Features in Silicon for MEMS and Wafer Level Packaging Applications. *J. Phys.: Conf. Ser.* **2006**, *34*, 271–276.

(32) Dixit, P.; Vahanen, S.; Salonen, J.; Monnoyer, P. Effect of Process Gases on Fabricating Tapered Through-Silicon vias by Continuous  $SF_6/O_2/Ar$  Plasma Etching. *ECS J. Solid State Sci. Technol.* **2012**, *1*, 107–116.

(33) Tezcan, D. S.; De Munck, K.; Pham, N.; Luhn, O.; Aarts, A.; De Moor, P.; Baert, K.; Van Hoof, C. In Development of Vertical and Tapered via Etch for 3D through Wafer Interconnect Technology, Electronics Packaging Technology Conference, 2006, EPTC'06, 8th ed.; IEEE, 2006; pp 22–28.

(34) Kimukin, I.; Islam, M. S.; Williams, R. S. Surface depletion thickness of p-doped silicon nanowires grown using metal-catalysed chemical vapour deposition. *Nanotechnology* **2006**, *17*, S240–S245.

(35) Williams, K. R.; Gupta, K.; Wasilik, M. Etch rates for micromachining processing-part II. J. Microelectromech. Syst. 2003, 12, 761–778.

(36) Pal, P.; Singh, S. S. A New Model for the Etching Characteristics of Corners Formed by Si{111} Planes on Si{110} Wafer Surface. *Engineering* **2013**, *05*, 1–8.

(37) Wang, Y.; Kang, Y.; Zhao, W.; Yan, S.; Zhai, P.; Tang, X. Studies on surface damage induced by ion bombardment. *J. Appl. Phys.* **1998**, 83, 1341–1344.

(38) Kumaravelu, G.; Alkaisi, M. M.; Bittar, A.; Macdonald, D.; Zhao, J. Damage studies in dry etched textured silicon surfaces. *Curr. Appl. Phys.* **2004**, *4*, 108–110.

(39) Mayet, A. S.; Cansizoglu, H.; Gao, Y.; Kaya, A.; Ghandiparsi, S.; Yamada, T.; Wang, S.-Y.; Islam, M. S. In Inhibiting device degradation induced by surface damages during top-down fabrication of semiconductor devices with micro/nano-scale pillars and holes, SPIE Conference Nanoscience+Engineering, SPIE, 2016; pp 99240C– 99240C7.

(40) Yamada, T.; Bauschlicher, C. W.; Partridge, H. Substrate for atomic chain electronics. *Phys. Rev. B: Condens. Matter Mater. Phys.* **1999**, 59, 15430.

(41) Mavrokefalos, A.; Han, S. E.; Yerci, S.; Branham, M. S.; Chen, G. Efficient light trapping in inverted nanopyramid thin crystalline silicon membranes for solar cell applications. *Nano Lett.* **2012**, *12*, 2792–6.

(42) Prasad, T.; Colvin, V. L.; Mittleman, D. M. The effect of structural disorder on guided resonances in photonic crystal slabs studied with terahertz time-domain spectroscopy. *Opt. Express* 2007, 15, 16954–16965.

(43) Yota, J. Effects of deposition method of PECVD silicon nitride as MIM capacitor dielectric for GaAs HBT technology. *ECS Trans.* **2011**, 35, 229–240.